# Electronics Image Stabilization, EIS

## 1. REVISION HISTORY

| Revision Date | Revision | Description                                   |

|---------------|----------|-----------------------------------------------|

| 01/28/2014    | 1.0      | Initial Release                               |

| 08/19/2014    | 2.0      | Added additional implementations / merged app |

|               |          | notes                                         |

#### 2. PURPOSE

Electronic Image Stabilization is a jitter compensation method for a video stream. The source of the jitter is typically natural hand motion, which is detected by a gyroscope and sent to an ISP (image signal processor). The ISP uses the direction and displacement of the hand movement provided by the gyro to crop the target video frame (for example 1080 x 1920 full HD) from a location in opposite direction from a high-resolution image sensor on the next frame to compensate for the jitter. A key element in successful compensation is synchronizing the gyro samples for a given frame to the exact frame it was for in a video stream. The synchronization often gets more complicated as ISPs vary the frame rate due to system overhead and lighting condition to maintain best exposure.

InvenSense gyroscopes, optimized for image stabilization, employ a method to ease such synchronization between gyro samples using a FSYNC (Frame Sync) pin and FIFO that stores tagged samples for each frame. This application note describes the use of ITG-3521, a 3-axis gyroscope optimized for image stabilization with very low noise and high sensitivity for EIS using FSYNC. There is also a mode during which gyro data can be read directly from gyro sensor register (no need for FSYNC and FIFO) using interrupt (section 7.3).

#### 3. RELATED DOCUMENTS

The following documents are recommended to fully understand the products and systems described in this application note:

- InvenSense ITG-3521 Datasheet

- InvenSense ITG-3521 Register Map

### **C**ONTENTS

| 1. | revision history                                                       | 1  |

|----|------------------------------------------------------------------------|----|

| 2. | Purpose                                                                | 1  |

| 3. | Related Documents                                                      | 1  |

| 4. | Implementations                                                        | 3  |

| •  | FIFO + FSYNC + INT                                                     | 3  |

| •  | FIFO + FSYNC                                                           | 3  |

| •  | Gyro Data Register + INT                                               | 3  |

| •  | Bus speed / type                                                       | 3  |

| 5. | EIS system block diagrams                                              | 4  |

| •  | FIFO + FSYNC + INT / FIFO + FSYNC                                      | 4  |

| •  | Gyro Data Register + INT                                               | 5  |

| 6. | Timing Diagram of FSYNC (FIFO+FSYNC+INT / FIFO+FSYNC)                  | e  |

| 7. | Recommended registers values                                           | e  |

| •  | Common settings for all three methods                                  | e  |

|    | 71. Full-Scale Range (FSR) Setting                                     | 6  |

|    | 72. Low-Pass Filter (DLPF) Setting                                     | 6  |

|    | 73. Output Data Rate (ODR) Setting                                     | 7  |

| •  | FIFO + FSYNC + INT / FIFO + FSYNC methods                              | 7  |

|    | FIFO and FSYNC Settings for both FIFO+FSYNC+INT and FIFO+FSYNC methods | 7  |

|    | Interrupt setting for FSYNC+FIFO+INT mehtod                            | 8  |

|    | Register 0x37, INT_PIN_CFG                                             | 8  |

|    | Register 0x38, INT_ENABLE                                              | 8  |

|    | Register 0x3A, INT_STATUS                                              | 8  |

| •  | Gyro data register + interrupt method                                  | 8  |

| 8. | Register Summary                                                       | 10 |

| •  | FIFO + FSYNC + INT                                                     | 10 |

| •  | FIFO + FSYNC                                                           | 11 |

| •  | Register + INT                                                         | 12 |

### 4. IMPLEMENTATIONS

There are several ways to implement an EIS enabled system. Each implementation includes various tradeoffs. This application note will describe three implementations:

- FIFO + FSYNC + INT

- FIFO + FSYNC

- Gyro Data Register + INT

#### FIFO + FSYNC + INT

The FIFO + FSYNC + INT method utilizes the gyroscope sensor FIFO to buffer sensor data and FSYNC data internally and generates an interrupt to the AP when a full video frame is complete. This allows the application processor to be interrupt driven and lowers the overhead in the application processor (or video processor) by concatenating the FSYNC with the gyroscope sensor data.

#### FIFO + FSYNC

The FIFO + FSYNC method is similar to the method above with the only difference being a polled implementation instead of an interrupt driven implementation.

#### GYRO DATA REGISTER + INT

The register + INT method bypasses the sensor FIFO buffer and FSYNC concatenation and instead generates an interrupt when sensor data is available and the application or image processor takes responsibility for all of the synchronization.

# BUS SPEED / TYPE

The ITG-3521 supports both an I2C and SPI interconnect to the applications processor. However, it is critical to understand the nature of the data rate and data rates to determine the correct implementation for a given implementation. Sampling rates above 1 KHz will require the use of the SPI interconnect to avoid bus overflow.

#### 5. EIS SYSTEM BLOCK DIAGRAMS

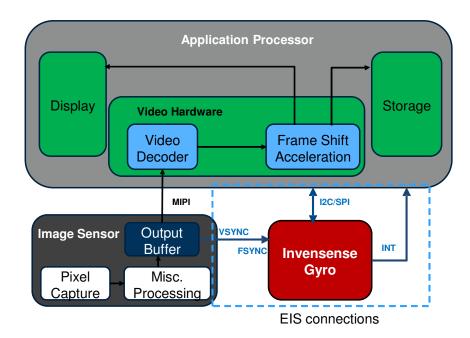

# • FIFO + FSYNC + INT / FIFO + FSYNC

For either the FIFO + FSYNC + INT method or the FIFO + FSYNC method, the block diagram below shows how Invensense's ITG-3521 connects to the image sensor and Application Processor, AP. In the case of FIFO + FSYNC the INT line is not connected. The VSYNC signal generated by an image sensor connects to the FSYNC input pin of ITG-3521. In the INT implementation, this signal is used to trigger an interrupt signal to the AP, letting it know the gyro data for a complete frame is ready to be read from the ITG-3521 FIFO. The data is then transferred through I2C/SPI bus to the AP.

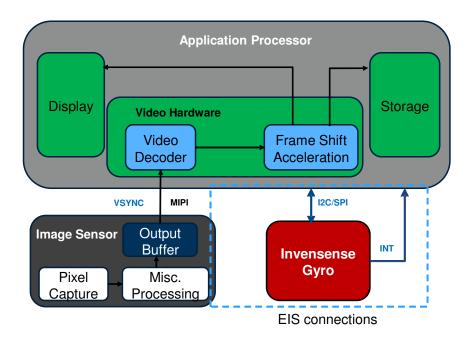

#### GYRO DATA REGISTER + INT

For either the Register + INT method, the block diagram below shows how Invensense's ITG-3521 connects to the Application Processor, AP. In this case, the AP is responsible for the synchronization of the VSYNC and gyroscope data. The VSYNC is part of the MIPI interface from the image sensor. The gyroscope connects to the AP via the I2C/SPI interface and generates an interrupt when new data is available.

# 6. TIMING DIAGRAM OF FSYNC (FIFO+FSYNC+INT / FIFO+FSYNC)

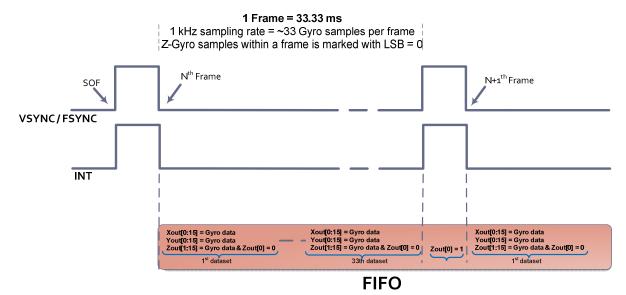

The rising edge of VSYNC indicates the Start of the Frame, SOF. Let us consider an example. If the frame rate is 30 frames per second, the frame length is going to be 33.333 ms as shown in Figure 1. The sampling rate for the ITG-3521 data is set to 1 kHz in this example. With this sampling rate at each frame length, we would have 33.333 frames or 33 frames for simplicity. The gyro data for all three axes, X, Y, and Z can be stored in FIFO through the register setting, explained in section 7.1. The value of FSYNC signal can be sampled and stored as LSB value in any of the Xout, Yout, or Zout data registers. In the example below (Figure 1), we are storing the sampled value of the FSYNC signal in Zout[0]. When the value of the FSYNC is low, the value "0" is stored in Zout[0] and when FSYNC is high, the value "1" is stored in Zout[0]. This value can be stored in Xout[0] or Yout[0] as well. When AP reads out the FIFO upon receiving an interrupt, all the read data with LSB equaling "0" is considered generated for a single frame. In the example below, the AP reads the FIFO content which has ~30 sample sets of gyro outputs corresponding to Xout[15:0], Yout[15:0], Zout[15:1], and Zout[0] = 0 for 30 images in a single frame. We will discuss how to set up the internal registers of ITG-3521 to enable this operation in the next section. Please note that in FIFO+FSYNC there is no need for an interrupt signal as shown in Figure 1 and the AP manages reading the FIFO data. Additionally the sampled FSYNC signal will lag the true FSYNC input by up to one ODR period.

Figure 1. Timing Diagram

#### 7. RECOMMENDED REGISTERS VALUES

As mentioned earlier there are three methods to read the ITG-3521 data.

Section 7.1 explains the settings that are in common for all the three methods. Section 7.2 explains the FIFO+FSYNC+INT/FIFO+FSYNC methods and Section 7.3 discusses the gyro data register method with interrupt.

#### COMMON SETTINGS FOR ALL THREE METHODS

#### 7..1. FULL-SCALE RANGE (FSR) SETTING

#### Register 0x1B, GYRO\_CONFIG

**FS SEL** (GYRO\_CONFIG [3:4]): For EIS applications using ITG-3521, these bits should be set to "11" to achieve recommended full-scale range (FSR) of ±250 dps, providing the widest range for EIS.

#### 7...2. LOW-PASS FILTER (DLPF) SETTING

#### Register 0x1B, GYRO\_CONFIG and 0x1A, CONFIG

The first setting at 1Khz ODR and 184Hz LPF will work for most applications. Higher ODR and LPF setting maybe selected to achieve the precision that the target application may require.

| Sampling Rate | DLPF BW | <u>FCHOICE_B</u> (GYRO_CONFIG[1:0]) | <u>DLPF_CFG</u> (CONFIG [2:0]) |

|---------------|---------|-------------------------------------|--------------------------------|

| 1 kHz         | 184 Hz  | 00                                  | 001                            |

| 8 kHz  | 250 Hz  | 00 | 000 |

|--------|---------|----|-----|

| 32 kHz | 8.8 kHz | x1 | xxx |

| 32 kHz | 3.6 kHz | 10 | xxx |

#### 7..3. OUTPUT DATA RATE (ODR) SETTING

#### Register 0x19, SMPLRT\_DIV

**SMPLRT\_DIV**[7:0]: The gyroscope output rate can be divided by value of this register to generate a reduced sample rate. Recommend sample rate is 1 kHz with a digital low-pass filter (DLPF) setting of 184 Hz. This configuration is achieved by setting proper bits at DLPF\_CFG[0:2] = 001 (register 0x1A) and FCHOICE\_B[1:0] = 00 (register 0x1B).

With above setting, the SMPLRT\_DIV divider is bypassed.

# FIFO + FSYNC + INT / FIFO + FSYNC METHODS

In these methods, the tagged gyro data is stored in FIFO. The FSYNC is used to tag the data based on the logic level of the signal (V-Sync) connected to FSYNC pin of ITG-3521. The V-Sync is signal provided by image sensors to indicate the start or end of a video frame. The value of the signal connected to FSYNC can be sampled and stored as the LSB value in any of Xout, Yout, or Zout data registers. Checking the tags by AP provides an extra level of data validation that the read out gyro data corresponds to an active V-sync signal. In the FIFO+FSYNC method, the FIFO has to be read by the AP often enough to prevent overflowing of the data. Based on 512 byte FIFO available in ITG-3521, the read out intervals are indicated below:

| Sampling Rate | FIFO Reading Interval | # of FIFO reads / second |

|---------------|-----------------------|--------------------------|

| 1 kHz         | 85 ms                 | 12                       |

| 8 kHz         | 10.625 ms             | 93                       |

| 32 kHz        | 2.66 ms               | 375                      |

#### FIFO AND FSYNC SETTINGS FOR BOTH FIFO+FSYNC+INT AND FIFO+FSYNC METHODS

#### • Register 0x1A, CONFIG

**FIFO\_MODE** (CONFIG [6]): By setting this bit to "0," additional writes will be written to the FIFO, replacing the oldest data.

**EXT\_SYNC\_SET** (CONFIG [5:3]): An external signal connected to the FSYNC pin can be sampled by configuring these bits.

Signal changes to the FSYNC pin are latched so that short strobes may be captured. The latched FSYNC signal will be sampled at the sampling rate defined in registers 0x19 and 0x1A (1 kHz). After sampling, the latch will reset to the current FSYNC signal state. The sampled value will be reported in place of the least significant bit in a sensor data register determined by the value of EXT\_SYNC\_SET according to the following table.

| EXT_SYNC_SET | FSYNC Bit Location |

|--------------|--------------------|

| 2 ("010")    | GYRO_XOUT_L[0]     |

| 3 ("011")    | GYRO_YOUT_L[0]     |

| 4 ("100")    | GYRO ZOUT L[0]     |

Figure 2.

#### Register 0x6A, USER CTRL

**FIFO\_EN** (USER\_CTRL[6]): Setting this bit to "1" enables FIFO operations.

#### Register 0x23, FIFO EN

**XG\_FIFO\_EN** (FIFO\_EN[6]): By setting this bit to "1", the X Gyro data will be loaded into the FIFO buffer.

YG \_FIFO\_EN (FIFO\_EN[5]): By setting this bit to "1", the Y Gyro data will be loaded into the FIFO buffer.

**ZG\_FIFO\_EN** (FIFO\_EN[4]): By setting this bit to "1", the Z Gyro data will be loaded into the FIFO buffer.

They are sampled at the sample rate defined in 0x19 and 0x1A registers.

#### Register 0x74, FIFO Read Write

FIFO DATA (FIFO R W [0:7]): The content of the FIFO can be read from this register.

#### INTERRUPT SETTING FOR FSYNC+FIFO+INT MEHTOD

#### Register 0x37, INT\_PIN\_CFG

**INT\_OPEN** (INT\_PIN\_CFG [6]): Setting the value of this bit to "0" means INT pin is configured as push-pull. Setting it to "1" means the INT pin is open drain.

LATCH\_INT\_EN (INT\_PIN\_CFG [5]): This bit has to be set to "0" to allow INT pin to emit a 50 μs long pulse.

**INT\_RD\_CLEAR** (INT\_PIN\_CFG [4]): This bit has to be set to "0" to enable clearing the INT only by reading INT STATUS of register 0x3A.

**FSYNC\_INT\_LEVEL** (INT\_PIN\_CFG [3]): When this bit is equal to "0", the logic level for the FSYNC pin (when used as an interrupt to the host processor) is active high. When this bit is equal to "1", the logic level for the FSYNC pin (when used as an interrupt to the host processor) is active low.

**FSYNC\_INT\_MODE\_EN** (INT\_PIN\_CFG [2]): When this bit is equal to 1, the FSYNC pin will trigger an interrupt when it transitions to the level specified by FSYNC\_INT\_LEVEL. When a FSYNC interrupt is triggered, the FSYNC\_INT bit in Register 0x3A will be set to 1. An interrupt is sent to the host processor if the FSYNC interrupt is enabled by the FSYNC\_INT\_EN bit in Register 0x38.

#### Register 0x38, INT\_ENABLE

**FSYNC\_INT\_EN** (INT\_ENABLE [3]): This bit has to be set to "1" to enable the FSYNC pin to be used as an interrupt to the host processor.

FIFO\_OFLOW\_EN (INT ENABLE [4]): This bit should be set to "0".

**DATA\_RDY\_EN** (INT\_ENABLE [0]): This bit should be set to "0".

#### Register 0x3A, INT\_STATUS

**FSYNC\_INT** (INT\_ENABLE [3]): This bit automatically sets to 1 when an FSYNC interrupt has been generated. The bit clears to 0 after the registers have been read.

**FIFO\_OFLOW\_INT** (INT\_STATUS [4]): This bit should be set to "0".

**DATA\_RDY\_INT** (INT\_STATUS [0]): This bit should be set to "0".

#### GYRO DATA REGISTER + INTERRUPT METHOD

#### Register 0x6A, USER\_CTRL

**I2C\_IF\_DIS** (USER\_CTRL[4]): This bit has to be set to "1" to enable SPI operations.

#### Register 0x37, INT PIN CFG

**INT\_OPEN** (INT\_PIN\_CFG [6]): Setting the value of this bit to "0" means the INT pin is configured as push-pull. Setting it to "1" means the INT pin is open drain.

**LATCH\_INT\_EN** (INT\_PIN\_CFG [5]): This bit has to be set to "0" to allow INT pin to emit a 50  $\mu$ s long pulse when sampling at 1 kHz or 8 kHz and 16  $\mu$ s long pulse when sampling at 32 kHz.

**INT\_RD\_CLEAR** (INT\_PIN\_CFG [4]): This bit has to be set to "0" to enable clearing the INT only by reading INT\_STATUS of register 0x3A.

#### Register 0x38, INT ENABLE

**DATA\_RDY\_EN** (INT\_ENABLE [0]): This bit should be set to "1". The Data Ready interrupt occurs when all the sensor registers have been written with the latest gyro sensor data

**FSYNC\_INT\_EN** (INT\_ENABLE [3]): This bit has to be set to "0" to disable the FSYNC signal to generate an interrupt.

FIFO\_OFLOW\_EN (INT\_ENABLE [4]): This bit should be set to "0".

#### • Register 0x3A, INT\_STATUS

**DATA\_RDY\_INT** (INT\_STATUS [0]): This bit automatically sets to 1 when a Data Ready interrupt has been generated. The bit clears to 0 after the registers have been read.

FSYNC\_INT (INT\_ENABLE [3]): This bit should be set to "0"

**FIFO\_OFLOW\_INT** (INT\_STATUS [4]): This bit should be set to "0".

# 8. REGISTER SUMMARY

• FIFO + FSYNC + INT

|                           | 6 3 3      |                                                   |                |                                     |               |                                                  |                   |                                      |              |                   |                |                                                                                    |                   |                   | ΞŽ              |      |                   |                                              |

|---------------------------|------------|---------------------------------------------------|----------------|-------------------------------------|---------------|--------------------------------------------------|-------------------|--------------------------------------|--------------|-------------------|----------------|------------------------------------------------------------------------------------|-------------------|-------------------|-----------------|------|-------------------|----------------------------------------------|

|                           | 6A         |                                                   | 3A             |                                     | 38            |                                                  | 37                |                                      | 23           |                   | 1B             |                                                                                    | 1A                |                   | 19              |      | ADDR<br>(HEX)     |                                              |

|                           | USER_CTRL  |                                                   | INT_STATUS     |                                     | INT_ENABLE    |                                                  | INT_PIN_CFG       |                                      | FIFO_EN      |                   | GYRO_CONFIG    |                                                                                    | CONFIG            |                   | SMPLRT_DIV      | NAME |                   |                                              |

| Enable FIFO<br>Enable I2C | R/W        | Generate INT on FSYNC<br>Clear INT status on read | R/W            | FSYNC to trigger an interrupt to AP | R/W           | INT Level is active high, open drain, pulse mode | R/W               | X, Y and Z gyro data written to FIFO | R/W          | FSR = +/- 250 dps | R/W            | FIFO overwrites allowed FSYNC stored in Zout(0) DLPF = 184 Hz and 1Khz sample rate | R/W               | Recommended Value | R/W             |      | SERIAL IF / VALUE | FIFO + FSYNC + INT Method – Recommended Regi |

|                           | -          | -                                                 | -              | -                                   | -             | 1                                                | INT_LEVEL         | 0                                    | TEMP_FIFO_EN | -                 | -              | •                                                                                  | -                 | 0                 |                 | 7    |                   | · INT Me                                     |

| 1                         | FIFO_EN    |                                                   | -              | -                                   | -             | 1                                                | INT_OPEN          | 1                                    | XG_FIFO_EN   | -                 | -              | 0                                                                                  | FIFO_MODE         | 0                 |                 | 6    |                   | ethod –                                      |

|                           |            |                                                   | -              | •                                   |               | 0                                                | LATCH_INT_EN      | 1                                    | YG_FIFO_EN   | -                 |                | 1                                                                                  |                   | 0                 |                 | 5    |                   | Recomi                                       |

| 0                         | I2C_IF_DIS | 0                                                 | FIFO_OFLOW_INT | 0                                   | FIFO_OFLOW_EN | 0                                                | INT_RD_CLEAR      | 1                                    | ZG_FIFO_EN   | 1                 | FS_SE          | 0                                                                                  | EXT_SYNC_SET[2:0] | 0                 | SMPLRT_DIV[7:0] | 4    | ВІТ               | mended F                                     |

|                           | -          | 1                                                 | FSYNC_INT      | 1                                   | FSYNC_INT_EN  | 1                                                | FSYNC_INT_LEVEL   | -                                    | -            | 1                 | FS_SEL[1:0]    | 0                                                                                  |                   | 0                 | iV[7:0]         | 3    |                   | legister S                                   |

|                           | -          |                                                   | -              |                                     | -             | 1                                                | FSYNC_INT_MODE_EN | 1                                    | -            | -                 | -              | 0                                                                                  | DLPF_CFG[2:0]     | 0                 |                 | 2    |                   | ister Settings                               |

|                           |            |                                                   |                |                                     |               | 1                                                |                   |                                      |              | 0                 |                | 0                                                                                  | FG[2:             | 0                 |                 | 1    |                   |                                              |

|                           | 1          | 0                                                 | DATA_RDY_INT   | 0                                   | DATA_RDY_EN   |                                                  | -                 | 1                                    | -            | 0                 | FCHOICE_B[1:0] | 1                                                                                  | [כ                | 0                 |                 | 0    |                   |                                              |

# • FIFO + FSYNC

|                           | 6A         |                                                   | 3A             |                                     | 38            |        | 37                |                                      | 23           |                   | 18             |                                                                                    | 1A                |                   | 19              |          | ADDR<br>(HEX)     |                                                   |

|---------------------------|------------|---------------------------------------------------|----------------|-------------------------------------|---------------|--------|-------------------|--------------------------------------|--------------|-------------------|----------------|------------------------------------------------------------------------------------|-------------------|-------------------|-----------------|----------|-------------------|---------------------------------------------------|

|                           | USER_CTRL  |                                                   | INT_STATUS     |                                     | INT_ENABLE    |        | INT_PIN_CFG       |                                      | FIFO_EN      |                   | GYRO_CONFIG    |                                                                                    | CONFIG            |                   | SMPLRT_DIV      | NAM<br>E |                   |                                                   |

| Enable FIFO<br>Enable I2C | R/W        | Generate INT on FSYNC<br>Clear INT status on read | R/W            | FSYNC to trigger an interrupt to AP | R/W           | No INT | R/W               | X, Y and Z gyro data written to FIFO | R/W          | FSR = +/- 250 dps | R/W            | FIFO overwrites allowed FSYNC stored in Zout(0) DLPF = 184 Hz and 1Khz sample rate | R/W               | Recommended Value | R/W             |          | SERIAL IF / VALUE | FIFO + FSYNC Method – Recommended Register Settin |

| 1                         | -          | -                                                 | -              | 1                                   | -             | 0      | INT_LEVEL         | 0                                    | TEMP_FIFO_EN | 1                 | -              | -                                                                                  | -                 | 0                 |                 | 7        |                   | IC Meth                                           |

| 1                         | FIFO_EN    |                                                   | -              | •                                   | -             | 0      | INT_OPEN          | 1                                    | XG_FIFO_EN   | -                 | -              | 0                                                                                  | FIFO_MODE         | 0                 |                 | 6        |                   | od – Re                                           |

| 1                         | -          |                                                   | -              |                                     | -             | 0      | LATCH_INT_EN      | 1                                    | YG_FIFO_EN   | -                 | -              | 1                                                                                  |                   | 0                 |                 | 5        |                   | comme                                             |

| 0                         | I2C_IF_DIS | 0                                                 | FIFO_OFLOW_INT | 0                                   | FIFO_OFLOW_EN | 0      | INT_RD_CLEAR      | 1                                    | ZG_FIFO_EN   | 1                 | FS_SI          | 0                                                                                  | EXT_SYNC_SET[2:0] | 0                 | SMPLRT_DIV[7:0] | 4        | ВІТ               | nded Reg                                          |

| 1                         | 1          | 0                                                 | FSYNC_INT      | 0                                   | FSYNC_INT_EN  | 1      | FSYNC_INT_LEVEL   | 1                                    | -            | 1                 | FS_SEL[1:0]    | 0                                                                                  |                   | 0                 | )IV[7:0]        | 3        |                   | ister Sett                                        |

|                           |            |                                                   | -              |                                     | -             | 0      | FSYNC_INT_MODE_EN |                                      | -            | -                 | -              | 0                                                                                  | DLPF_CFG[2:0]     | 0                 |                 | 2        |                   | ings                                              |

|                           |            |                                                   | -              |                                     | -             |        | -                 |                                      | -            | 0                 |                | 0                                                                                  | CFG[2             | 0                 |                 | 1        |                   |                                                   |

|                           |            | 0                                                 | DATA_RDY_INT   | 0                                   | DATA_RDY_EN   | 1      | 1                 | ,                                    | 1            | 0                 | FCHOICE_B[1:0] | 1                                                                                  | :0]               | 0                 |                 | 0        |                   |                                                   |

## • REGISTER + INT

|                             | 6A         |                                                   | 3A             |                                     | 38            |                                                  | 37                |                                      | 23           |                   | 1B             |                                                                                    | 1A                |                   | 19              |   | ADDR<br>(HEX)     |                                                       |

|-----------------------------|------------|---------------------------------------------------|----------------|-------------------------------------|---------------|--------------------------------------------------|-------------------|--------------------------------------|--------------|-------------------|----------------|------------------------------------------------------------------------------------|-------------------|-------------------|-----------------|---|-------------------|-------------------------------------------------------|

|                             | USER_CTRL  |                                                   | INT_STATUS     |                                     | INT_ENABLE    |                                                  | INT_PIN_CFG       |                                      | FIFO_EN      |                   | GYRO_CONFIG    |                                                                                    | CONFIG            |                   | SMPLRT_DIV      |   | NAME              |                                                       |

| Disable FIFO<br>Enable ISPI | R/W        | Generate INT on FSYNC<br>Clear INT status on read | R/W            | FSYNC to trigger an interrupt to AP | R/W           | INT Level is active high, open drain, pulse mode | R/W               | X, Y and Z gyro data written to FIFO | R/W          | FSR = +/- 250 dps | R/W            | FIFO overwrites allowed FSYNC stored in Zout(0) DLPF = 184 Hz and 1Khz sample rate | R/W               | Recommended Value | R/W             |   | SERIAL IF / VALUE | REGISTER + INT Method – Recommended Register Settings |

| ı                           | -          | 1                                                 | -              | 1                                   | -             | 1                                                | INT_LEVEL         | 0                                    | TEMP_FIFO_EN | -                 | -              |                                                                                    | -                 | 0                 |                 | 7 |                   | NT Met                                                |

| 0                           | FIFO_EN    | -                                                 | -              | -                                   | -             | 1                                                | INT_OPEN          | 1                                    | XG_FIFO_EN   | -                 | -              | 0                                                                                  | FIFO_MODE         | 0                 |                 | 6 |                   | nod – R                                               |

| -                           | -          | -                                                 | -              | -                                   | -             | 0                                                | LATCH_INT_EN      | 1                                    | YG_FIFO_EN   | -                 | -              | 1                                                                                  |                   | 0                 |                 | 5 |                   | ecomm                                                 |

| 1                           | I2C_IF_DIS | 0                                                 | FIFO_OFLOW_INT | 0                                   | FIFO_OFLOW_EN | 0                                                | INT_RD_CLEAR      | 1                                    | ZG_FIFO_EN   | 1                 | FS_SEL[1:0]    | 0                                                                                  | EXT_SYNC_SET[2:0] | 0                 | SMPLRT_DIV[7:0] | 4 | ВІТ               | ended Re                                              |

|                             | -          | 0                                                 | FSYNC_INT      | 0                                   | FSYNC_INT_EN  | 1                                                | FSYNC_INT_LEVEL   | -                                    | -            | 1                 | L[1:0]         | 0                                                                                  |                   | 0                 | iV[7:0]         | 3 |                   | gister Set                                            |

| ı                           |            |                                                   | -              |                                     | -             | 1                                                | FSYNC_INT_MODE_EN | -                                    | -            | -                 | -              | 0                                                                                  | DLPF_CFG[2:0]     | 0                 |                 | 2 |                   | tings                                                 |

| 1                           |            |                                                   |                |                                     |               | 1                                                |                   |                                      |              | 0                 |                | 0                                                                                  | CFG[2:            | 0                 |                 | 1 |                   |                                                       |

| 1                           | -          | 1                                                 | DATA_RDY_INT   | 1                                   | DATA_RDY_EN   |                                                  | -                 | -                                    | -            | 0                 | FCHOICE_B[1:0] | 1                                                                                  | 0]                | 0                 |                 | 0 |                   |                                                       |

This information furnished by InvenSense is believed to be accurate and reliable. However, no responsibility is assumed by InvenSense for its use, or for any infringements of patents or other rights of third parties that may result from its use. Specifications are subject to change without notice. InvenSense reserves the right to make changes to this product, including its circuits and software, in order to improve its design and/or performance, without prior notice. InvenSense makes no warranties, neither expressed nor implied, regarding the information and specifications contained in this document. InvenSense assumes no responsibility for any claims or damages arising from information contained in this document, or from the use of products and services detailed therein. This includes, but is not limited to, claims or damages based on the infringement of patents, copyrights, mask work and/or other intellectual property rights.

Certain intellectual property owned by InvenSense and described in this document is patent protected. No license is granted by implication or otherwise under any patent or patent rights of InvenSense. This publication supersedes and replaces all information previously supplied. Trademarks that are registered trademarks are the property of their respective companies. InvenSense sensors should not be used or sold in the development, storage, production or utilization of any conventional or mass-destructive weapons or for any other weapons or life threatening applications, as well as in any other life critical applications such as medical equipment, transportation, aerospace and nuclear instruments, undersea equipment, power plant equipment, disaster prevention and crime prevention equipment.

©2014 InvenSense, Inc. All rights reserved. InvenSense, MotionTracking, MotionProcessing, MotionProcessor, MotionFusion, MotionApps, DMP, and the InvenSense logo are trademarks of InvenSense, Inc. Other company and product names may be trademarks of the respective companies with which they are associated.

©2014 InvenSense, Inc. All rights reserved.